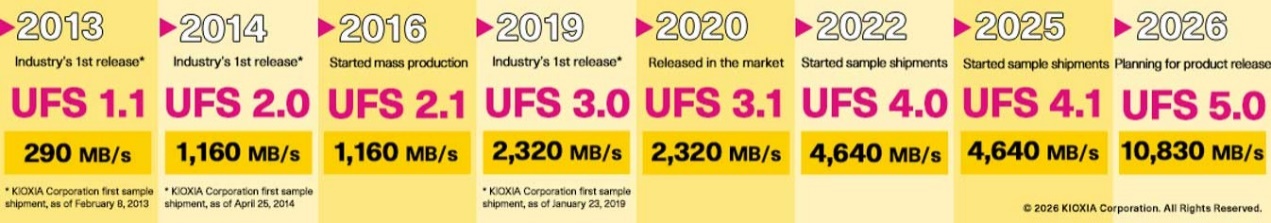

随着铠侠陆续向客户提供UFS 5.0评估样品,移动端跨入UFS 5.0时代不过是时间的问题。UFS 5.0相比UFS 4.0和UFS 4.1拥有非常明显的优势,其传输速度可达10.8GB/s,是UFS 4.1 4.64GB/s的两倍以上,让移动端可以轻而易举跨入10GB/s的传输速率大关,与PC端的PCIe 5.0 SSD速度看齐。

更快的传输速率势必带来更好的体验,同时也让端侧AI(On-Device AI)变成了可能。更确切的说,UFS 5.0为更为广阔的端侧AI应用提供了扎实的硬件基础。

规格的质变

光从规格来看,铠侠UFS 5.0已经带来了显著突破,该产品目前提供512GB和1TB两种容量规格,采用当下广受欢迎的第八代BiCS FLASH技术,并提供7.5x13mm的封装规格,能够轻松的装入手机、平板甚至是智能穿戴设备中。

其中第八代BiCS FLASH广受各厂商欢迎,被应用于许多品牌消费级和企业级SSD中,同时也是构建UFS产品的重要基础。第八代BiCS FLASH采用218层3D NAND堆叠技术,存储密度达到18.3Gb/mm²,在同类技术中处于世界领先水平,也一举将BiCS FLASH的I/O接口速度最高提升至3.6Gbps。

在晶圆直接键合到存储阵列(CBA)技术加持下,第八代BiCS FLASH可以将CMOS控制电路与存储单元阵列分别在不同晶圆上制造,已获得更高的效率,随后两个晶圆通过高精度键合,进而构建出具备高性能、高能效和高密度的优秀产品。

铠侠UFS 5.0在第八代BiCS FLASH的基础上,还采用了MIPI M-PHY 6.0 + UniPro 3.0协议,这是铠侠在标准制定初期就深度参与并率先开发高速接口,通过优化电源设计,让UFS 5.0可以同时满足高性能、低功耗的表现。

UFS 5.0使用了PAM4(Pulse Amplitude Modulation 4-Level)的多电平信号调制技术,PAM4可以在每个传输信号中可以携带更多信息,帮助UFS 5.0实现10.8GB/s的传输速度。但PAM4也对噪声更为敏感,也需要更为优秀的控制器和链路信号设计才能最大程度发挥闪存性能。

铠侠UFS 5.0在MIPI UniPro 3.0协议层引入了多项增强的数据完整性保护机制,通过高性能控制器实现链路均衡(Link Equalization)、独立电源轨设计以及通过预编码(Pre-coding)和格雷编码(Grey Encoding)实现高性能传输下信号的准确性,实现UFS 5.0更快、更稳的特点。

为端侧AI加码

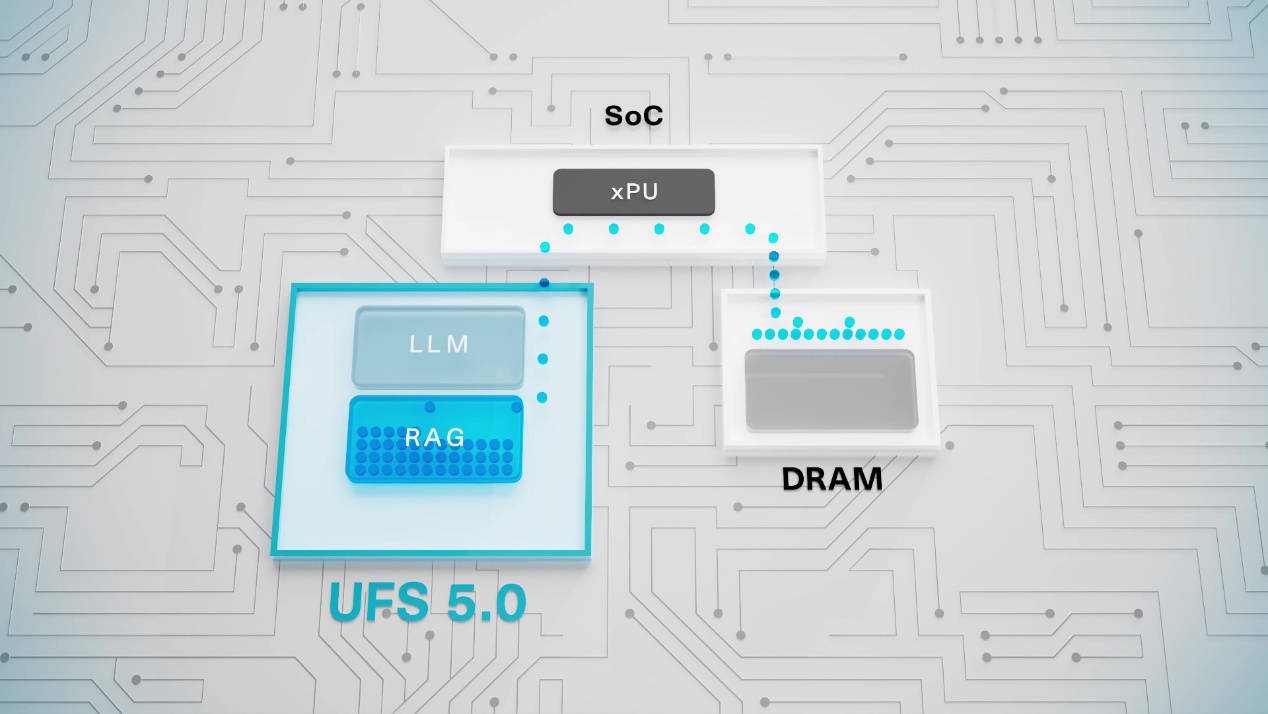

有了高性能、高可靠性的UFS 5.0,端侧运行更高要求的生成式AI变成了可能。以智能手机为例,运行生成式AI通常需要两个步骤。第一步是将LLM从UFS加载到DRAM,UFS读取性能将直接影响到”Time to First Token”,即“用户收到首个响应的时间”。第二步是SoC从DRAM读取LLM参数进行推理运算。

当前端侧LLM大约在30-40亿个参数,对应FP8量化精度大约在3GB到4GB左右,随着模型参数增加,加载时间延长,用户体验将会明显下降。

凭借着大容量和高性能,铠侠UFS 5.0可以将LLM容量支持范围提升到10GB,FP8量化精度相当于100亿个参数。由于UFS 5.0天生的高速传输,”Time to First Token”也会明显缩短,能够更好的提升用户体验。

不仅如此,铠侠UFS 5.0与铠侠AiSAQ搭配,在UFS中存储RAG(检索增强生成)专用数据库,释放DRAM,也进而让体验更为顺畅。

当端侧AI无需过分依赖云端,便具有了保护隐私和实时响应的优势。铠侠UFS 5.0的推出将无疑显著提升了智能手机的端侧AI能力。通过BiCS FLASH,MIPI M-PHY 6.0和UniPro 3.0协议,10.8GB/s速率,以及优秀的主控和(AiSAQ)固件设计,铠侠UFS 5.0从物理层、协议层、存储层和应用层全方面提升了端侧的使用体验,为AI的进一步普及奠定了扎实的基础。

京公网安备 11010202008829号

京公网安备 11010202008829号